آینده فناوری CMOS

فهرست مطالب

- چکیده

- مقدمه

- تاریخچه CMOS ، گذشته ، حال و آینده

- چگالی توان و مقیاس گذاری ولتاژ

- اثرات تصادفی وجود ناخالصی ها در مقیاس نانومتر

- کانال بخش بندی شده

- اولین نظریه پیاده سازی اطلاعات کوانتومی بر بستر سلیکون

- روش های پیاده سازی اطلاعات کوانتومی

- انواع روش های پیاده سازی کیوبیت

- پیاده سازی کیوبیت با استفاده از ترانزستور های CMOS

- نتیجه گیری

چکیده

فناوری ساخت CMOS هرساله بصورت تصاعدی در حال بهبود است ، که این موضوع را می توان در حوزه های کوچک سازی و به حداقل رسانی اندازه و سایز ترانزیستور ، کاهش مصرف و توان و همچنین افزایش سرعت و پردازش اشاره نمود.

امروزه با به کار گیری گرافین برای ساخت مدارات CMOS به نتایج بسیار شگفت انگیزی دست یافته ایم ، محققان و مهندسی شرکت IBM با استفاده از گرافین سی سی ( سلیکون کاربید ) و ویفر پوشیده شده با گرافین ، موفق به ساخت ترانزیستوری شده اند که ده هزار بار سریعتر از نمونه معمولی آن که فقط سلیکون می باشد است ، در این فن آوری که نام این فناوری را طراحی سه بعدی یا Non Planar ، منسوب کرده اند.

این روش جایگیزن طراحی CMOS های معمولی یا مسطح خواهد شد ، اما با این حال جایگزین نمودن Si CMOS با نوع جدید آن بسیار دشوار می باشد.

از طرف دیگر بتازگی محققان انگلیسی با استفاده از ترانزیستور CMOS موفق به ساخت کیوبیت برای کامپیوترهای کوانتومی شدند.

آنها از یک نوسان ساز برای رویت حالت های مختلف در کیوبیت ها استفاده کردند ، فرناندو گنزالس زالبا سرپرست تیم تحقیقاتی از آزمایشگاه کمبریج هیتاچی در این خصوص میگوید : “ما قصد داشتیم به همگان نشان دهیم که می توان از این فناوری برای تولید کامپیوترهای کوانتومی استفاده کرد “.

این گروه تحقیقاتی با استفاده از گیت ترانزیستور های CMOS ، اقدام به ایجاد یک کیوبیت CMOS کردند.

با این روش ، امکان تولید کیوبیتهای سیلیکونی مبتنی بر CMOS ، فراهم گردید.

مقدمه

با مقیاس گذاری فناوری CMOS از کسری از میلی متر نا چند نانومتر در فناوری های امروزی ، شاهد پیشرفت شگفت انگیزی طی سالیان اخیر هستیم.

استفاده از فناوری جدید Non-Planar(3D) باعث افزایش سرعت ، کاهش ابعاد ، کاهش مصرف و توان در مدارات مبتنی بر این تکنولوژی خواهیم شد که همه اینها با استفاده از ماده نستبا جدید گرافین میسر خواهد شد.

گرافین دارای خواص بسیار شگفت انگیزی است که بشرح ذیل می باشد :

- دارای خاصیت جذب کنندگی بسیار بالای الکترون یا حرکت حفره ها

- ساختار مسطح

- هدایت حرارتی بسیار بالا

- ظرفیت تحمل جریان های بالا

- و قابلیت فشرده سازی و کوچک سازی ابعاد

تمامی این موارد برای طراحی یک CMOS با کارایی بالا مناسب و حائز اهمیت می باشد.

در گام دیگری از توسعه فناوری CMOS ها، ظهور فناوری دیگری که ساخت کیوبیت ، با استفاده از CMOS می باشد را شاهد می باشیم.

این تکنولوژی باعث می شود ترانزیستور های CMOS وارد عرصه جدیدتری گردند ، لذا آینده کامپیوترهای کوانتومی احتمالا چندان تفاوتی با سیستمهای فعلی نداشته باشد به طوری که همگان بتوانند از این سیستمها استفاده کنند.

تاریخچه CMOS ، گذشته ، حال و آینده

با اتصال دو قطبی اکسید فلز و اثر میدان در نیمه هادی ها ، ترانزستور های MOSFET با به عرصه ظهور گماردند ، که دارای ویژگی های مهمی از جمله :

- سرعت بالاتر

- ولتاژ کاری کم

- مصرف انرژی بهینه

را می توان اشاره نمود.

همانطور که میدانیم دو نوع ترانزیستور MOS وجود دارد ، ترانزستور PMOS و ترانزیستور NMOS ، اما هرکدام از این نوع ترانزستور ها برای مدار های دیجیتال دارای اشکالات خاصی هستند از جمله اینکه درنوع P ما شاهد عبور 1 منطقی کامل هستیم اما صفر منطقی به خوبی عبور داده نمی شود و برعکس در نوع N ما شاهد عبور صفر منطقی بطور کامل و یک ناقص هستیم ، علت این مشکل ، تاثیر ولتاژ آستانه بر Srource-Drain می باشد ، از این روی راه حل های مختلفی ارائه گردید تا اینکه پس از دهه ها فرانک وانلاس منطق جدیدی به نام CMOS را ارائه نمود.

در این منطق با استفاده از هر دو نوع P و N که بصورت مکمل در طراحی دیجیتال استفاده می شوند توانست مشکل اصلی استفاده از ترانزستور های MOS را مرتفع سازد ، علاوه بر آن موفق گردید نویز پذیری را کاهش و همچنین مصرف توان ایستا را نیز کاهش دهد.

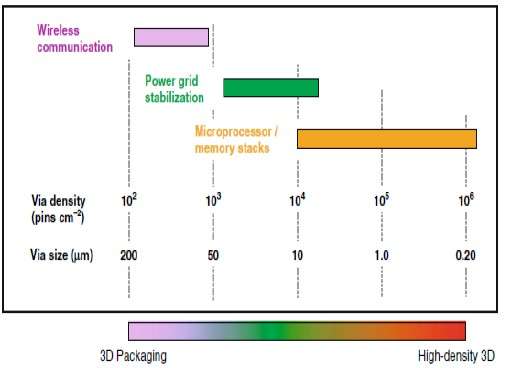

در زیر روند توسعه این فناوری را که بصورت مسطح می باشد می توان مورد بررسی قرار داد :

شکل 1 – روند کوچک سازی در خصوص فناوری های MOS, HCMOS

برای ساخت یک چیپ با استفاده از فناوری CMOS می بایست با استفاده از مواد نیمه هادی و تزریق ناخالصی به آنها کار را شروع کرد ، برای این منظور طراح می بایست مراحل زیر را دنبال نماید :

- لیتوگرافی

- ساختار فیزیکی

- قوانین طراحی و مقیاس بندی

مواد نیمههادی در معرض فرایندهای مختلفی قرار می گیرند که در آن ناخالصی ها و مواد دیگری به آن اضافه میشوند.

مدار مجتمع یک شبکه الکترونیکی است که بر روی یک قطعه از مواد نیمههادی ساخته شدهاست. چندین مرحله برای ساخت آن وجود دارد که از جمله می توان به موارد ذیل اشاره نمود :

- لیتوگرافی

- ساختار فیزیکی

- دنباله ساخت CMOS

- قواعد طراحی

- فرآیند CMOS پیشرفته و مقیاس بندی فنی

لیتوگرافی Lithography :

فرآیندی است که برای انتقال الگوهای شبکه الکترونیکی به هر لایه از IC استفاده میشود.

در گام بعدی ما ترتیب ساخت را خواهیم داشت که در آن ویفر سیلیکون از نوع P شروع فرآیند ساخت می باشد.

مرحله اول در ساخت CMOS رشد epitaxial است ، لایه epi به عنوان یک لایه پایه برای طراحی دیجیتال استفاده میشود ، بعد از آن n – well یا چاه تشکیل میشود.

ناحیه فعال، ناحیهای است مسطح که در آن ترانزیستورهای CMOS ساخته و یک لایه نازک از SiO2 غنی شده با نیترید سیلیکون روی آن را پوشانده است.

اگر بخواهیم به اختصار مراحل لیتوگرافی را بر شماریم می توانیم به این موارد اشاده نماییم :

- رشد اکسید گیت

- رسوب پولی سیلیکون

- تشکیل PMOS

- تشکیل NMOS

- تثبیت و ساخت یک مدار مجتمع

با استناد به شکل یک انتظار می رود فناوری CMOS همچنان راه درازی را در پیش روی داشته باشد ، در اوایل سال ۱۹۷۰ ، CMOS با استفاده از فنآوری مسطح (Planar 2D) طراحی شد.

اما پیروی از قانون مور که کوچک سازی و افزایش سرعت به همراه استفاده از تکنولوژی های جدید است امری ضروری و بسیار مهم است.

برای این منظور فنآوری Non-Planar 3D برای طراحی مدارات مجتمع CMOS پا به عرصه ظهور گمارده است .

اما چالش مسئله از آنجا شروع می شود که ما نمی توانیم از همه نمیه هادی ها برای ساخت ترانزیستورهای ماسفت استفاده نماییم.

برای این منظور دانشمندان این حوزه با استفاده از گرافین که ماده نسبتا جدیدی محسوب می شوند توانستند مسائل مربوط به این چالش بزرگ را تا حد بسیار زیادی مرتفع نمایند.

از همین روی گرافین و III – V / Ge در سطح وسیعتری از تکنولوژی سهبعدی استفاده میشوند ، اما مواد III – V به دلیل ویژگی سوییچینگ از تکنولوژی ۲ بعدی به فنآوری ۳ بعدی ، عملکرد و سرعت بهتر با مساحت کوچکتر را بدون مقیاس گذاری ، تغییر نخواهند داد.

مزیت استفاده از تکنیک سهبعدی نه تنها افزایش چگالی CMOS بر روی یک چیپ است بلکه دارای مزایای دیگری مانند:

- فنآوری مدارهای ترکیبی (به عنوان مثال دیجیتال و آنالوگ)

- فنآوریهای پردازش ترکیبی (به عنوان مثال دو قطبی و CMOS) و ترکیبی از مواد نیمه هادی مختلف است

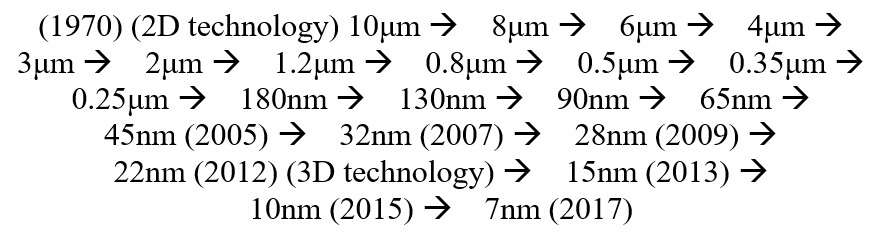

در ترکیب ۳ بعدی ، چگالی بسته بندی از دستگاه به دستگاه ، کم و زیاد می شود.

این نمودار محدوده تکنولوژی ۳ بعدی را نشان میدهد:

شکل ۲ – نمودار نشان میدهد که طیف وسیعی از کاربردهای تکنولوژی ۳ بعدی در IBM در حال اجرا است

پس از HCMOS , CMOS (CMOS سرعت بالا ) معرفی گردید ، از آنجا که CMOS های معمولی با چالشهای بسیاری مواجه هستند ، که از جمله آن ها می توان به این موارد اشاره نمود :

- جریان نشت در گیت

- جراین نشت مابین Source و Drain

- عدم قابلیت اطمینان پذیری پشته گیت و افت جریان کانال در فرکانس ها ی بالا

- نشتی از انتقال سطح به سطح و مقاومت بالا دسترسی به Source-Drain

از همین روی با استفاده از فنآوریهای پیشرفته ای که از مواد دی الکتریک سرعت بالا بجای SiO2 استفاده می کنند به منظور بهنیه سازی فناوری CMOS و توسعه آن در آینده استفاده خواهد شد.

شکل 3 – روند افزایش عملکرد ( HP ) در توسعه فناوری CMOS

مواد مختلف بکار رفته شامل موارد ذیل می باشد :

ضریب دیالکتریک سرعت بالا ، Ge ، III – V و ترانزیستور با فناوری ساخت 3D برای بهبود میزان عملکرد ، چگالی و مقیاس بندی توان اجرایی CMOS می باشد.

از همین روی پژوهشگران بدنبال مواد دی الکتریک سرعت بالا ، موفق به کشف ماده جدید تری به نام hfo2 شدند.

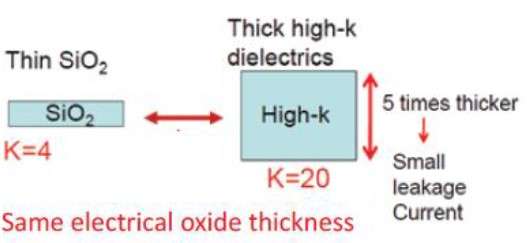

یکی از خواص هیجان انگیز استفاده از hfo2 به جای دی اکسید سلیسیم افزایش 5 برابری ضخامت فیزیکی برای همان مقدار خواص الکتریکی در مقایسه با دی اکسید سلیسیم می باشد.

شکل 4 – کاهش قابل توجه مقدار نشتی جریان در گیت با استفاده از جایگزین نمودن دی الکتریک سرعت بالا بجای اکسید سیلیسیم

شکل 5 – افزایش 5 براری ضخامت فیزیکی دی الکتریک سرعت بالا در مقایسه با SiO2

چگالی توان و مقیاس گذاری ولتاژ

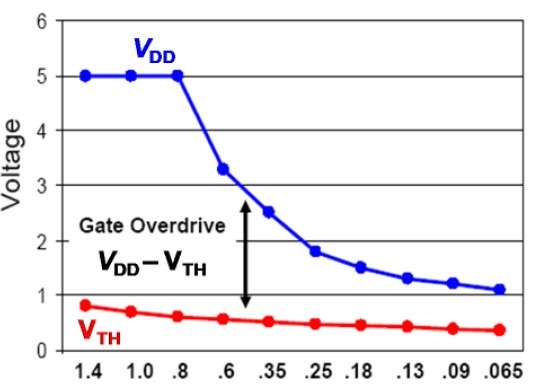

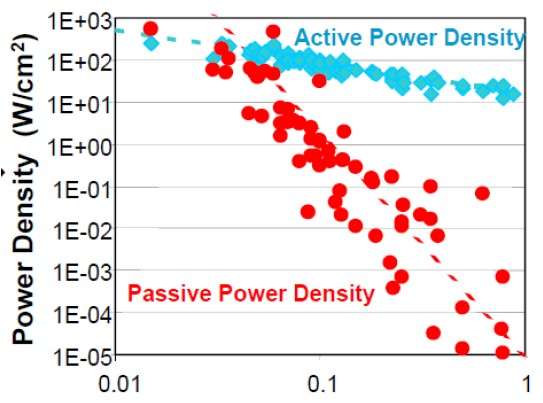

بطور میانگین طبق قانون مور که در بالاتر اشاده شد ، تراکم و سرعت ترانزیستور های CMOS در هر 18 ماه دو برابر می گردد ، اما ولتاژتغذیه به این نسبت کاهش نیافته است بنابر این سوالی که در ذهن ما مطرح میشود این است که چگونه و چرا قدرت افزایش مییابد؟

جواب این سئوال در کاهش فضای بیهوده و افزایش مقیاس فرکانس کاری است اگر Vdd مقیاس بندی نشده باشد.

روشهای مختلفی که برای کاهش انرژی به کار میرود که باعث حل مسئله و Reformulation یا دوباره فرموله کردن مسائل می گردد.

از آنجا که ترانزیستور در حال خاموش نیز دچار نشتی است با استفاده از تکنیک و پیاده سازی مکانیزم ، نشت پایین بر ، می توان بر این مسئله در طراحی تراشه ها فائق آمد ، لذا مکانیزم نشت پایین بر ، شامل سوییچها و سلولهای زیر است :

- سیگنال کنترل سوئیچ

- سوئیچهای توکار و ردیف هایی از سلولهای استاندارد

شکل 6 – مقیاس گذاری ولتاژ CMOS

شکل 7 – چگالی توان در مقابل طول کانال

اثرات تصادفی وجود ناخالصی ها در مقیاس نانومتر

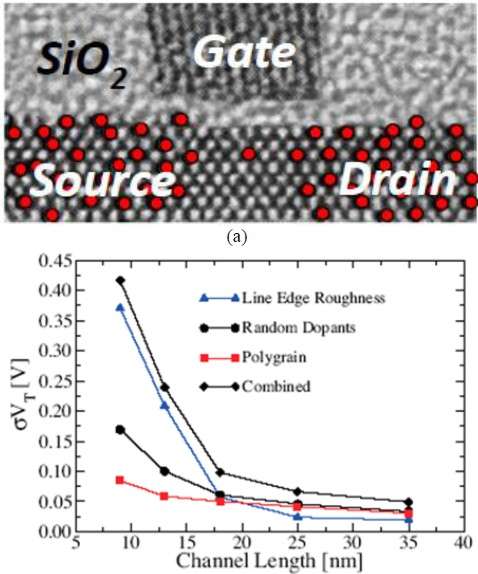

چنانچه در فرآیند ساخت CMOS ها مقادیر اندکی ناخالصی وجود داشته باشد باعث تغییرات در ولتاژ آستانه یعنی Vt می شود این بدان معنی است که تعداد و مکان اتم های ناخالص باعث تغییرات تصادفی در ولتاژ آستانه ترانزیستور (Vth) می شود که به آن اثر ناخالصی تصادفی می گویند.

شکل 8 – ( a ) ترانزیستور MOS با اتمهای ناخالص ( b ) تغییرات در ولتاژ آستانه

کانال تقسیم شده در MOSFET

کانال بخش بندی شده

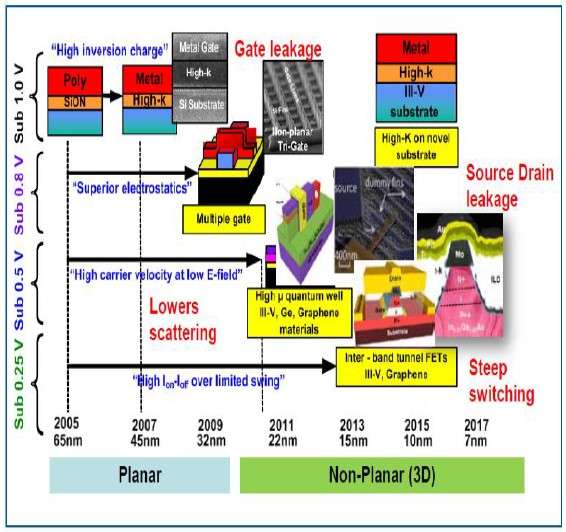

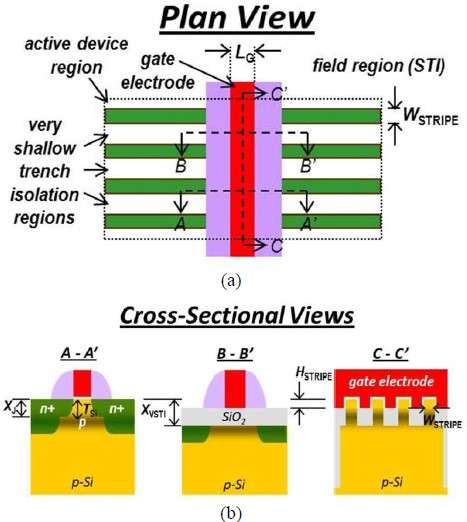

در این نوع طراحی MOSFET , کانال شامل خطوطی راه راه با عرضی معادل با width > (Lg) است که توسط لایه بسیار نازک نارسانا Very Shallow Trench Isolation که مخفف آن ( VSTI ) ، محافظت و تفکیک شده است.

لایه VSTI در مقایسه با ترانزیستورهای معمولی STI دارای ضخامت بسیار کم تری می باشد به همین منظور این بخش بندی در ناحیه Source-Drain ، و اتصال به زمین بکار نمی رود.

در طراحی VSTI به منظور کنترل کانال از طریق میدان های الکتریکی و افزایش آن می توان لایه کانال را با استفاده از دی الکتریک های فرکانس بالا تقویت نمود که باعث کاهش عرض میدان الکتریکی و در نتیجه نشتی کمتر در گیت خواهد شد.

شکل 9

اولین نظریه پیاده سازی اطلاعات کوانتومی بر بستر سلیکون

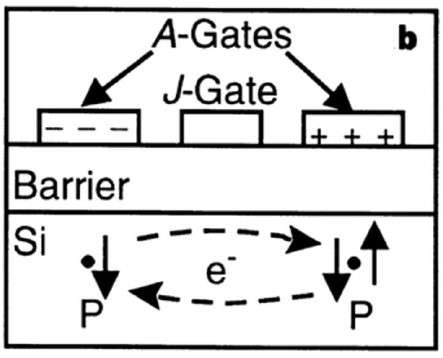

در سال 1998 مقاله ای در مجله نیچر منتشر گردید که طی آن بروس کین ایده قرار دادن آرایه ای از اتم های فسفر در داخل سیلیکن و روکش نمودن آن ها را با لایه ای عایق که در بالای آن آرایه ای از الکترود ها قرار گرفته اند را ارائه داد .

بر اساس این طرح هر کدام از الکترود ها می توانستند به اتم های لایه های پایین تر ولتاژ اعمال کنند.

شکل 10

روش های پیاده سازی اطلاعات کوانتومی

با وجود تمام مسائل مطرح شده در این مقاله برای به حداقل رسانی ابعاد ترانزیستور ها و افزایش توان پردازش و کاهش توان مصرفی آن ها اما می دانیم که سر انجام بدلیل محدودیت های بنیادین فیزیکی در خصوص کاهش سایز کوچک سازی تراشه ها به پایان خواهد رسید ، چرا که قوانین ساخت آنها متکی بر فیزیک کلاسیک است و این پاشنه آشیل در فرآیند های نانومتری خواهد بود ، زیرا می دانیم قوانین فیزیک کلاسیک در ابعاد های اتمی و نانومتری پاسخگو نیستند و میبایست در این حوزه با تکیه بر فیزیک کوانتوم بر این محدودیت ها غلبه نماییم.

این محدودیت ها باعث حذف فناوری ساخت نیمه رسانا ها نخواهد شد بلکه مبنای محاسباتی را در خصوص ساخت را تغییر خواهد داد که نتیجه آن ساخت تراشه های کوانتومی خواهد شد.

اولین گام برای ساخت یک تراشه کوانتومی ، ایجاد بیت کوانتومی یا کیوبیت بجای بیت باینری است.

ابزاری که از طریق آن بتوان مقدار بیت کوانتومی را خواند و یا تغییر داد ، اما چالش اصلی بیت های کوانتومی این است که بسیار ناپایدار می باشند و با کوچکترین تغییر ناخواسته ای مانند تغییر در میدان مغناطیسی و یا تغییر فتون ، مقادیر خود را از دست می دهند و یا تغییر می کنند.

زمان همدوستی :

مدت زمانی است که می توان داده ها را در کیوبیت ذخیره نمود.

انواع روش های پیاده سازی کیوبیت

- پیاده سازی با استفاده از یون های به دام افتاده :

در این روش یک یون 43Ca+ را از طریق میدان الکتریکی یا فرکانس های رادیویی محدود می کنند ، با اعمال یک میدان مغناطیسی متوسط به این یون ، تفکیک پذیری سطح انرژی بین دو ساختار فوق کوچک یون به اندازی بزرگ بود که تحت تاثیر موارد ناخواسته قرار نگیرد و بتواند مقادیر خود را حفظ نماید .

بنابر این یون 43Ca+ برای حفظ حالات کیوبیت کوچکتر از صفر و کوچکتر از یک بسیار ایده آل به نظر می رسد خصوصا اینکه زمان همدوستی آن در حدود 50 ثانیه می باشد که در نوع خود بسیار شگفت انگیز می باشد.

- پیاده سازی با استفاده از ابر رسانا :

بر اساس آن یک اتم مصنوعی بر روی یک تراشه سیلیکونی قرار می گیرد که در اثر اعمال جریان الکتریکی در خازن ها و نقاط اتصال ، دروازه و تونلی ایجاد می گردد.

- پیاده سازی بر مبنای اسپین :

بر اساس این طرح کیوبیت ها بر پایه اسپین و جهت چرخش الکترون ها به دور خود می توانند داده ها را ذخیره و نگهداری می نمایند.

شکل 11

پیاده سازی کیوبیت با استفاده از ترانزستور های CMOS

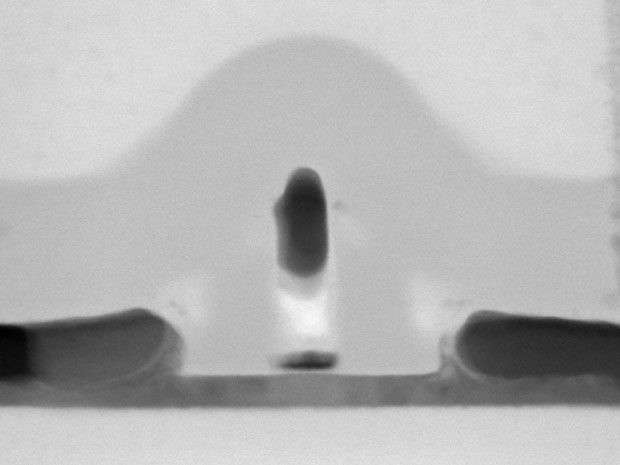

محققان در آزمایش خود توانستند با استفاده از ترانزیستورهای CMOS یک دروازه ای بوجود بیاورند که کانال را از طرفین احاطه کرده است که علاوه بر آن گوشه هایی با زاویه 90 درجه را تشکیل می داد .

این کانال کمی شبیه به مستطیل است که افقی بر روی صفحه سیلیکون قرار گرفته است ، از همین روی میدان الکتریکی در این گوشه ها قوی تر از سایر نقاط نانو سیم می باشد ، که این امر موجب می شود این گوشه همانند یک تله کوانتومی میدان الکتریکی را احاطه نماید و تشکیل یک dots کوانتومی نماید .

چنانچه دما به زیر 20 درجه کلوین تنزل یابد آنگاه یک الکترون می تواند بین این نقاط کوانتومی از طریق تونل سازی حرکت نماید.

بسته به این که چگونه الکترون بین این نقاط حرکت می کند ما می توانیم دو حالت کوانتومی مختلف داشته باشیم که به عنوان ” یک ” و ” صفر ” مقدار کوانتومی استفاده می شود.

با این حال, الکترون گرفتار شده را میتوان با استفاده از یک پالس ولتاژ سریع در گیت به هر حالت از بر هم نهی کوانتومی تغییر دهیم.

در این خصوص گونزالس نام این حالت کوانتومی را Coherence نهاده است و بیان نموده که این حالت می تواند تا ۱۰۰ پیکوثانیه به طول بیانجامد.

شکل 12

این دروازه همچنین اجازه خواندن حالت کوانتومی الکترون را در کانال خواهد داد .

برای این منظور محققان آن را به یک مدار LC متصل کردند که به آن فرکانس ۳۵۰ مگاهرتز اعمال شده بود .

زمانی که الکترون در یک گوشه دیگر باشد و یا در حالت برهم نهی کوانتومی قرار داشته باشد ، خازن دو نقطه کوانتومی کمی تغییر میکند , که باعث Detuning می گردد.

در حال حاضر زمان همدوستی در این فناوری در حدود ۱۰۰ پیکوثانیه است و محققان انتظار دارند که آن را به یک نانو ثانیه افزایش دهند ، این عملیات باید به اندازه کافی طولانی باشد تا عملیات مهمی مانند تصحیح خطا را بتوان انجام داد.

چنین عملیاتی مستلزم این است که دو یا تعداد بیشتری از qubits به چنین روشی متصل شوند که اندازهگیری چرخش یک qubit را بلافاصله تحتتاثیر قرار میدهد .

اگر دو ترانزیستور مشابه به اندازه کافی نزدیک هم قرار داده شوند ، یا در همان نانو سیم سیلیکونی نصب شوند ، بنابراین کوپلینگ الکترواستاتیک بین دو الکترون وجود دارد .

گونزالس میگوید : ” اگر شما عملیاتی را روی یک الکترون انجام دهید ، بر حالت کوانتومی دیگر الکترون در یک ترانزیستور جداگانه تاثیر خواهد گذاشت .

این عملیات مجموعه کاملی از عناصر مورد نیاز برای یک کامپیوتر کوانتومی را تکمیل خواهند کرد.

نتیجه گیری

سرعت گسترش و نفود تجهیزات دیجیتال روز به روز در حال افزاش است از همین روی نیاز به تجهیزات کوچکتر ، ارزان تر با مصرف توان بهینه شده و در عین حال کارایی بالاتر بیشتر احساس می شود.

دانشمندان همچنان در حال توسعه فناوری CMOS ها هستند استفاده از نیمه هادی هایی مانند گرافین و hfo2 و استفاده از دی الکتریک های سرعت بالا می توانند تاثیر چشمگیری در به حداقل رسانی ابعاد ، مصرف توان و افزایش سرعت سوئیچینگ داشته باشند ، اما در نهایت مسائل بنیادین فیزیک کلاسیک که نمی تواند رویداد های ابعاد زیر اتمی و سرعت های نزدیک به سرعت نور را توجیح نماید ، مانع از به حداقل رسانی هایی در ابعاد بسیار کوچک و زیر اتمی خواهد شد ، که در این صورت توسعه فناوری موجود به پایان خود خواهد رسید.

این مفهموم بدان معنی نیست که فناوری نیمه هادی ها به پایان راه خود رسیده است ، بلکه بدین معنی است که می توانیم با تغییر قوانین محاسباتی از فیزیک کلاسیک به فیزیک کوانتوم و بکارگیری و ارتقاء فناوری های نیمه هادی ها و خصوصا در موضوع این مقاله CMOS ها ، به سطح دیگری از فناوری دست یابیم که حاصل آن تولید تراشه های کوانتومی خواهد شد ، در آینده ای نچندان دور استفاده از کامپوتر های کوانتومی و چیپ ست های کوانتومی امری بدیهی و متعارف خواهد شد.

سرعت پردازش ها به سطح جدیدی از پردازش خواهند رسید و بسیاری از الگوریتم های رایج دچار تغییرات شگرفی خواهند شد.

هوش مصنوعی و اینترنت اشیاء با استفاده از فناوری کوانتومی وارد مرحله جدیدی از توسعه خواهند گردید ، لذا انتظار پدیده های بسیار پیچیده و خاصی را از تکنولوژی های پیش رو خواهیم داشت .

اینکه آینده بشر چگونه دستخوش فناوری های پردازش های کوانتومی و سیستم های هوشمند که مانند انسان به خودآگاهی رسیده باشند یکی از سئوالات بسیار مهم و مبهمی است که دانشمندان این حوزه هنوز پاسخ روشنی درباره آن ارائه نکرده اند ، به هر حال این مسیری است که دیر یا زود به وقوع خواهد پیوست و باید منتظر رویت فوائد و مضرات فناوری های بسیار مدرنی که در آینده ای بسیار نزدیک به آن می رسیم باشیم.